——Дељено од ДВИН Фроума

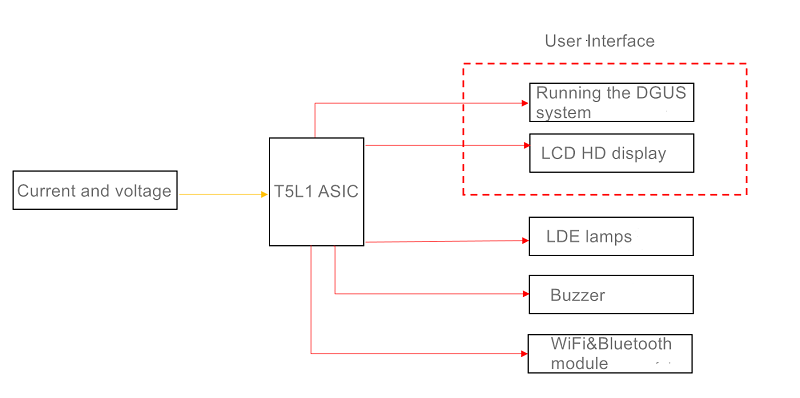

Користећи ДВИН Т5Л1 чип као контролно језгро целе машине, прима и обрађује додир, АДЦ аквизицију, ПВМ контролне информације и покреће ЛЦД екран од 3,5 инча за приказ тренутног статуса у реалном времену.Подржава даљинско подешавање осветљености ЛЕД извора светлости путем ВиФи модула и подржава гласовни аларм.

Карактеристике програма:

1. Усвојите Т5Л чип за рад на високој фреквенцији, АД аналогно узорковање је стабилно, а грешка је мала;

2. Подржава ТИП Ц директно повезан са рачунаром за отклањање грешака и снимање програма;

3. Подржава брзи ОС језгро интерфејс, 16-битни паралелни порт;УИ језгро ПВМ порт, излаз АД порта, јефтин дизајн апликације, нема потребе за додавањем додатног МЦУ-а;

4. Подржава ВиФи, Блуетоотх даљински управљач;

5. Подржава 5~12В ДЦ широк напон и широки опсег улаза

1.1 Шема дијаграма

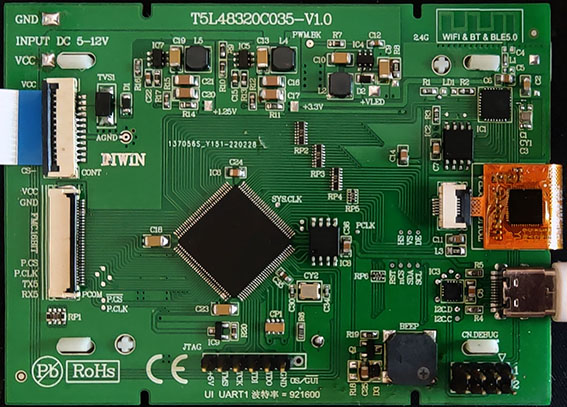

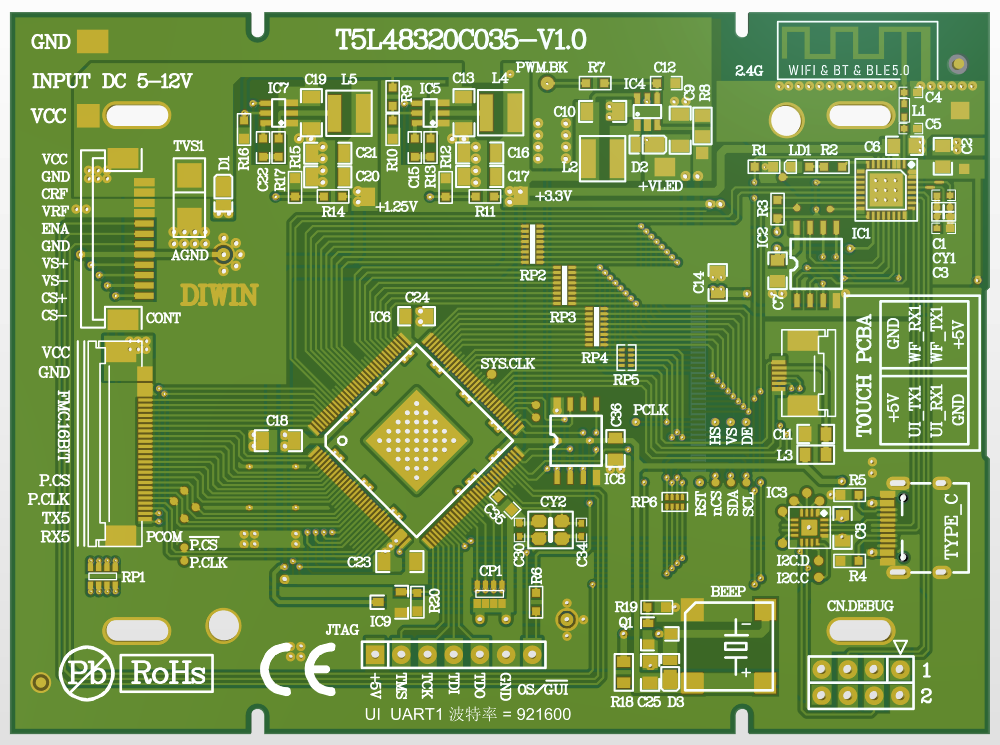

1.2 ПЦБ плоча

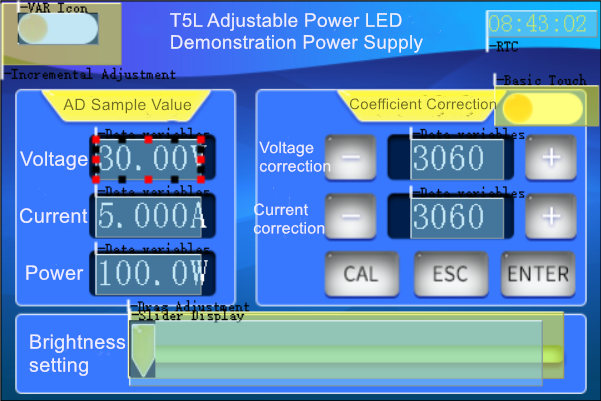

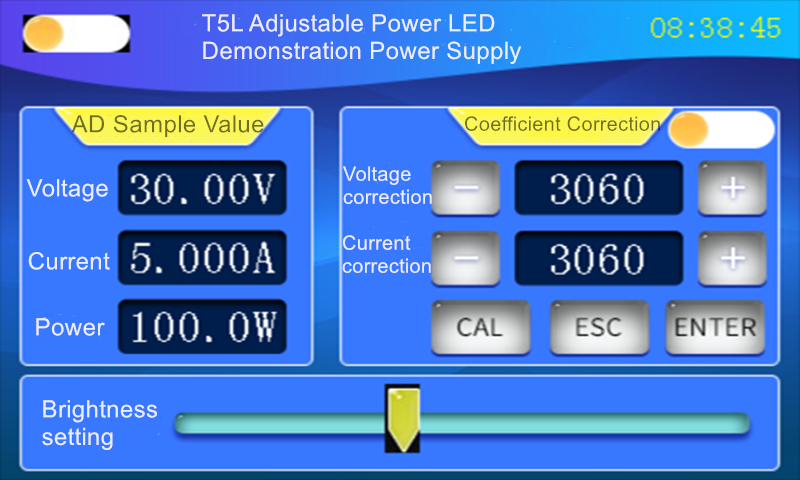

1.3 Кориснички интерфејс

Срамота увод:

(1) Дизајн хардверског кола

1.4 Шема кола Т5Л48320Ц035

1. МЦУ логичко напајање 3.3В: Ц18, Ц26, Ц27, Ц28, Ц29, Ц31, Ц32, Ц33;

2. МЦУ језгро напајања 1.25В: Ц23, Ц24;

3. МЦУ аналогно напајање 3.3В: Ц35 је аналогно напајање за МЦУ.Приликом слагања, уземљење језгра од 1,25 В и логичко уземљење могу се комбиновати заједно, али аналогно уземљење мора бити одвојено.Аналогно уземљење и дигитално уземљење треба да се сакупе на негативном полу ЛДО излазног великог кондензатора, а аналогни позитивни пол такође треба да се прикупи на позитивном полу ЛДО великог кондензатора, тако да се шум узорковања АД минимизира.

4. АД коло за аквизицију аналогног сигнала: ЦП1 је АД аналогни улазни филтер кондензатор.Да би се смањила грешка узорковања, аналогно и дигитално уземљење МЦУ-а су одвојене независно.Негативни пол ЦП1 мора бити повезан са аналогном земљом МЦУ-а са минималном импедансом, а два паралелна кондензатора кристалног осцилатора су повезана са аналогном земљом МЦУ-а.

5. Коло зујалице: Ц25 је кондензатор напајања за зујалицу.Зујалица је индуктивни уређај и током рада ће постојати вршна струја.Да би се смањио врх, потребно је смањити МОС погонску струју зујалице да би МОС цев радила у линеарном региону и дизајнирати коло тако да ради у режиму прекидача.Имајте на уму да Р18 треба да буде повезан паралелно на оба краја зујалице да би се подесио квалитет звука зујалице и да би звук зујалице био оштар и пријатан.

6. ВиФи коло: узорковање ВиФи чипа ЕСП32-Ц, са ВиФи+Блуетоотх+БЛЕ.На ожичењу, уземљење РФ напајања и уземљење сигнала су одвојени.

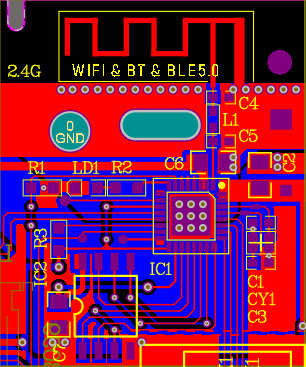

Дизајн 1.5 ВиФи кола

На горњој слици, горњи део бакреног премаза је петља за уземљење снаге.Петља уземљења рефлексије ВиФи антене мора имати велику површину до уземљења напајања, а тачка сакупљања уземљења напајања је негативни пол Ц6.Треба обезбедити рефлектовану струју између уземљења и ВиФи антене, тако да испод ВиФи антене мора бити бакарни премаз.Дужина бакреног премаза премашује дужину проширења ВиФи антене, а проширење ће повећати осетљивост ВиФи;тачка на негативном полу Ц2.Велика површина бакра може заштитити шум изазван зрачењем ВиФи антене.2 бакарна уземљења се одвајају на доњем слоју и скупљају на средњи јастучић ЕСП32-Ц кроз отворе.Уземљењу за РФ напајање је потребна нижа импеданса од петље за уземљење сигнала, тако да постоји 6 пролаза од уземљења за напајање до плочице чипа да би се осигурала довољно ниска импеданса.Петља уземљења кристалног осцилатора не може имати РФ снагу да тече кроз њу, иначе ће кристални осцилатор генерисати подрхтавање фреквенције, а померање ВиФи фреквенције неће моћи да шаље и прима податке.

7. Коло напајања ЛЕД позадинског осветљења: узорковање чипа драјвера СОТ23-6ЛЕД.ДЦ/ДЦ напајање за ЛЕД независно формира петљу, а ДЦ/ДЦ уземљење је повезано са 3.3В ЛОД уземљењем.Пошто је језгро ПВМ2 порта специјализовано, оно емитује 600К ПВМ сигнал, а додат је РЦ који користи ПВМ излаз као ОН/ОФФ контролу.

8. Опсег улазног напона: дизајнирана су два ДЦ/ДЦ степена смањења.Имајте на уму да отпорници Р13 и Р17 у ДЦ/ДЦ колу не могу бити изостављени.Два ДЦ/ДЦ чипа подржавају улаз до 18В, што је погодно за екстерно напајање.

9. УСБ ТИПЕ Ц порт за отклањање грешака: ТИП Ц може да се прикључи и искључи напред и назад.Уметање унапред комуницира са ВИФИ чипом ЕСП32-Ц за програмирање ВИФИ чипа;обрнуто уметање комуницира са КСР21В1410ИЛ16 за програмирање Т5Л.ТИП Ц подржава напајање од 5В.

10. Комуникација са паралелним портом: Т5Л ОС језгро има много слободних ИО портова, а може се дизајнирати комуникација са 16-битним паралелним портом.У комбинацији са СТ АРМ ФМЦ протоколом паралелног порта, подржава синхроно читање и писање.

11. ЛЦМ РГБ дизајн интерфејса велике брзине: Т5Л РГБ излаз је директно повезан са ЛЦМ РГБ, а отпор бафера је додат у средини да би се смањиле сметње ЛЦМ таласања воде.Приликом ожичења, смањите дужину везе РГБ интерфејса, посебно ПЦЛК сигнала, и повећајте тестне тачке РГБ интерфејса ПЦЛК, ХС, ВС, ДЕ;СПИ порт на екрану је повезан са П2.4~П2.7 портовима Т5Л, што је погодно за дизајнирање драјвера екрана.Водите РСТ, нЦС, СДА, СЦИ тестне тачке да бисте олакшали развој основног софтвера.

(2) ДГУС интерфејс

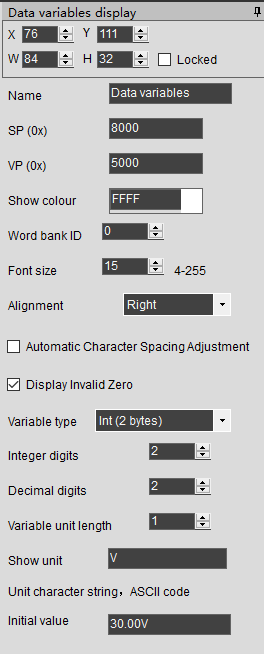

1.6 Контрола приказа променљивих података

(3) ОС

//———————————ДГУС формат за читање и писање

типедеф струцт

{

у16 аддр;//УИ 16-битна адреса променљиве

у8 датЛен;//8битдата ленгтх

у8 *пБуф;//8-битни показивач података

} УИ_пацкТипеДеф;//ДГУС читање и писање пакета

//————————————контрола приказа променљивих података

типедеф струцт

{

у16 ВП;

у16 Кс;

у16 И;

у16 Цолор;

у8 Либ_ИД;

у8 ФонтСизе;

у8 Алгнмент;

у8 ИнтНум;

у8 ДецНум;

у8 Типе;

у8 ЛенУинт;

у8 СтрингУинит[11];

} Нумбер_спТипеДеф;// структура описа променљиве података

типедеф струцт

{

Нумбер_спТипеДеф сп;//дефинише показивач описа СП

УИ_пацкТипеДеф спПацк;//дефинише СП променљиву ДГУС пакет за читање и писање

УИ_пацкТипеДеф впПацк;//дефинишемо вп променљиву ДГУС пакет за читање и писање

} Нумбер_ХандлеТипеДеф;// структура променљиве података

Са претходном дефиницијом ручке променљиве података.Затим дефинишите променљиву за приказ узорковања напона:

Нумбер_ХандлеТипеДеф Хсампле;

у16 волтаге_сампле;

Прво, извршите функцију иницијализације

НумберСП_Инит(&Хсампле,волтаге_сампле,0×8000);//0×8000 овде је показивач описа

//——Променљива података која показује иницијализацију структуре СП показивача——

воид НумберСП_Инит(Нумбер_ХандлеТипеДеф *број,у8 *вредност, у16 бројАддр)

{

број->спПацк.аддр = бројАддр;

број->спПацк.датЛен = сизеоф(број->сп);

број->спПацк.пБуф = (у8 *)&број->сп;

Реад_Дгус(&нумбер->спПацк);

број->впПацк.аддр = број->сп.ВП;

свитцх(нумбер->сп.Типе) //Дужина података вп променљиве се аутоматски бира према типу променљиве података дизајнираном у ДГУС интерфејсу.

{

случај 0:

случај 5:

број->впПацк.датЛен = 2;

пауза;

случај 1:

случај 2:

случај 3:

случај 6:

број->впПацк.датЛен = 4;

случај 4:

број->впПацк.датЛен = 8;

пауза;

}

број->впПацк.пБуф = вредност;

}

Након иницијализације, Хсампле.сп је показивач описа променљиве података узорковања напона;Хсампле.спПацк је комуникациони показивач између ОС језгра и променљиве података узорковања напона корисничког интерфејса преко функције ДГУС интерфејса;Хсампле.впПацк је атрибут промене променљиве података узорковања напона, као што је фонт Боје итд. се такође прослеђују језгру корисничког интерфејса преко функције ДГУС интерфејса.Хсампле.впПацк.аддр је адреса променљиве података узорковања напона, која је аутоматски добијена из функције иницијализације.Када промените променљиву адресу или променљиви тип података у ДГУС интерфејсу, нема потребе да ажурирате адресу променљиве у језгру ОС-а синхроно.Након што ОС језгро израчуна променљиву волтаз_сампле, потребно је само да изврши функцију Врите_Дгус(&Хсампле.впПацк) да би је ажурирала.Нема потребе за паковањем волтаге_сампле за ДГУС пренос.

Време поста: 15.06.2022